На встречах с представителями смежных предприятий после обсуждения рабочих моментов нередко звучит вопрос: «А как у вас организационно построен процесс проектирования, как осуществляется взаимодействие между разработчиками электрических схем, конструкторами, технологами, производственными и другими службами?». Взаимный обмен опытом позволяет перенять лучшее и увидеть собственные недоработки.

С усложнением стоящих перед предприятием задач, количественным и качественным ростом службы главного конструктора, обновлением парка производственного оборудования, внедрением информационных систем управления приобретают актуальность более широкая автоматизация проектных работ и тесная интеграция с вышеперечисленными инновациями.

В настоящей статье рассмотрены организационная и техническая составляющие результативной работы системы автоматического проектирования печатных плат (САПР ПП), приведены условия нацеленности ее на создание узлов с высокоскоростными интерфейсами, описана динамичная связь с IT-системами управления и с производством. Без сомнения, изложенные в статье принципы работы САПР ПП в целом характерны для большинства профильных предприятий.

Сегодня САПР ПП является основным инструментом разработчиков изделий электроники. Применяемая на предприятии система проектирования позволяет использовать в качестве коммутационных оснований печатные платы любой сложности – многослойные (Рис. 1), гибкие, гибко-жесткие (Рис. 2), платы СВЧ, платы со встроенным теплоотводом или с толстой медью. Алгоритмы трассировки печатных дорожек поддерживают выполнение требований современных высокоскоростных интерфейсов передачи данных – PCIe, SATA III, гигабитный Ethernet, LVDS, HDMI, DDR3/DDR4, USB3.0, DisplayPort и т. д.

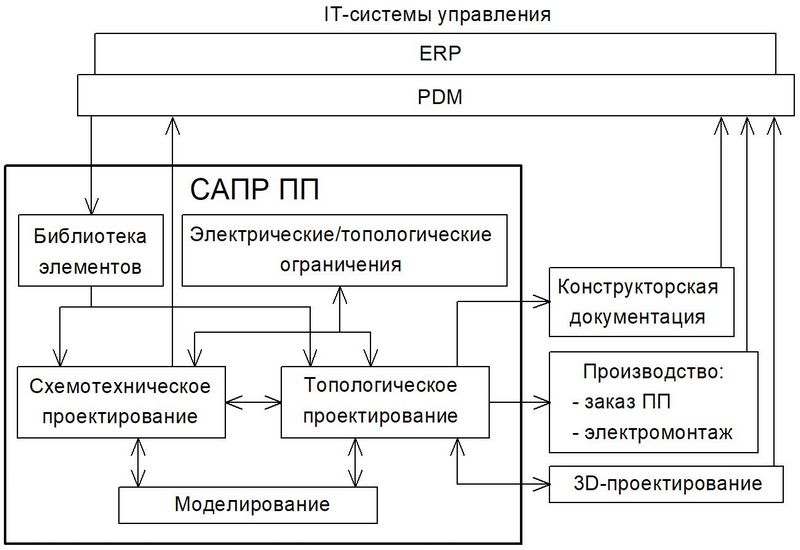

Любая система проектирования подразумевает совместную работу входящих программ в виде сквозного маршрута и активное взаимодействие со сторонними ресурсами. В случае САПР ПП основными составляющими являются библиотека элементов, редакторы электрических схем и топологии, модуль задания электрических и топологических ограничений, подпрограммы подготовки информации для выпуска конструкторской документации и генерации производственных данных для изготовления печатной платы и для автоматизированного монтажа компонентов. Также в состав современных корпоративных САПР ПП обязательно входят модули электрического и теплового моделирования, модули связи с САПР ПЛИС (программируемых логических интегральных схем), с механическими САПР (3D проектирование), а также инструменты интеграции с IT-системами управления (PLM/PDM и ERP системами). Укрупненный маршрут САПР ПП, используемый в АО «НТЦ ЭЛИНС», и его связи с другими ресурсами предприятия представлены на Рис. 3.

Созданная в САПР ПП центральная библиотека элементов едина для всех проектов. Доступ к ней ограничивается правами участников, которые разделены на две группы – узкоспециализированные библиотекари (с правами полного доступа), несущие персональную ответственность за применение элементов, соответствие их справочникам IT-систем управления, и остальные сотрудники, занятые непосредственно проектированием (с правами доступа только на чтение). Такой подход способствует повышению производительности труда за счет разграничения функций и позволяет более квалифицированно выполнять поставленные задачи.

Общее количество элементов библиотеки превышает 21 тыс. наименований. Библиотекари отвечают за достоверность и правильность оформления самого элемента и входящих в него составных частей – условного графического обозначения (УГО) для представления на электрической схеме и посадочного места для размещения на печатной плате.

Первоначальную заготовку УГО создает сотрудник, заказывающий новый элемент и представляющий удобство его подсоединения в будущей электрической схеме. Для многовыводных элементов допускается наличие нескольких УГО. Библиотекари проверяют правильность назначений «имя вывода – номер ножки корпуса», а также выполнение требований ЕСКД к оформлению УГО, обеспечивающее единый стиль и преемственность в различных проектах.

Посадочные места формируются библиотекарями в соответствии с требованиями общих технических нормативов, государственных/отраслевых стандартов и с требованиями технических условий/технических описаний на конкретные компоненты. Активно используется электронный калькулятор расчета посадочных мест для компонентов поверхностного монтажа (SMT компоненты) по требованиям стандарта IPC-7351. Тем самым сводятся к минимуму сомнения производства в правильности геометрических размеров контактных площадок и их взаимном расположении для качественной установки компонента на плату.

Полный библиотечный элемент объединяет УГО, посадочное место, а также информацию об эквивалентных (взаимозаменяемых) выводах и эквивалентных логических вентилях (типа И-НЕ). В обязательном порядке заполняются внутренние атрибуты элемента – системные (изначально имеющиеся в САПР ПП) и пользовательские (созданные на предприятии). Наличие атрибутов впоследствии облегчает работу, позволяет получать больше информации о входящих компонентах и о проекте в целом. Вновь созданные элементы проверяются библиотекарями в тестовом проекте для подтверждения их пригодности к рабочему проектированию и правильности содержимого атрибутов.

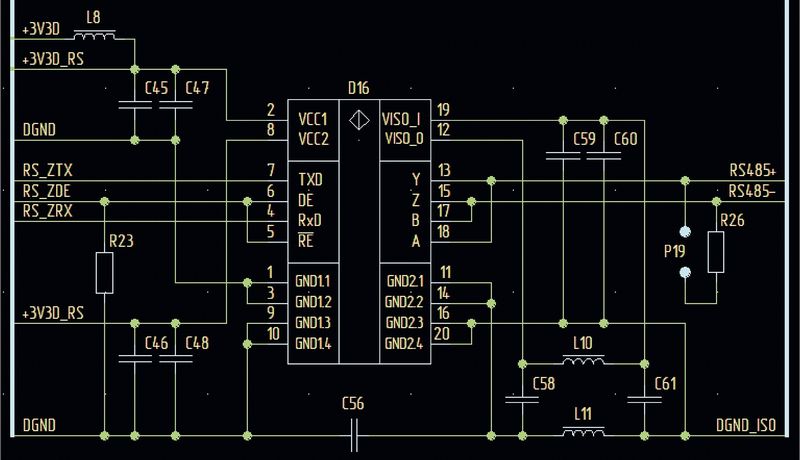

В современных САПР ПП схема электрическая и печатная плата обычно представлены в виде неразрывного целого, поэтому для удобства работы проекты размещают на сетевом сервере предприятия с полным доступом к нему участников (схемотехников и топологов). Это позволяет в процессе проектирования вносить доработки и изменения в схему при текущем состоянии топологии. В рамках одного проекта возможна поддержка нескольких электрических схем со своими печатными платами. Электрические схемы оформляются в полном соответствии с требованиями ЕСКД (Рис. 4), а связанные с ними перечни элементов и ведомости покупных изделий формируются PDM-системой автоматически в законченном виде из стандартного отчета о входящих компонентах, известном как bom-файл. Этот файл строится на основе внутренних атрибутов библиотечных элементов. Он же служит базой для формирования электронной заготовки конструкторской спецификации на узел. Поддерживаются методы единичного и группового оформления документации.

При схемотехническом проектировании реализована имеющаяся в САПР ПП возможность размещения элементов двумя способами: непосредственно из центральной библиотеки по имени элемента или из ее дубликата в виде табличной базы данных. Допускается комбинированное применение обоих способов.

Внутренние атрибуты библиотечных элементов, доступные в схемотехническом редакторе, позволяют в процессе проектирования быть информированным о текущем статусе компонента по его закупке, а также обращаться через гиперссылку к индивидуальной карточке компонента в PDM-системе. В карточке содержатся данные о применяемости компонента в других узлах (соответственно, в PDM-системе можно найти и посмотреть предыдущее схемотехническое решение и его топологическую реализацию), текущее количество свободных остатков на складе, наличие допустимых замен, файлы с технической информацией (выдержки из технических условий/технических описаний, стандарты скоростных интерфейсов, руководства по применению и пр.).

Вышеупомянутая табличная база данных (дубликат центральной библиотеки) наряду с внутренними атрибутами библиотечного элемента расширена собственными атрибутами, ориентированными на однотипные группы элементов, например:

Табличная база данных, при необходимости, в любой момент легко может быть дополнена новыми атрибутами. При работе с нею внутри электрической схемы возможна простая фильтрация данных по одному или нескольким атрибутам в заданных ограничивающих диапазонах для сужения результатов поиска и подбора необходимого библиотечного элемента по параметрам. Из табличной базы данных также можно обратиться к индивидуальной карточке компонента в PDM-системе до вынесения его на схему (например, для сравнения эксплуатационных параметров однотипных микросхем).

При создании электрических схем узлов с высокоскоростными интерфейсами разработчик, как правило, формирует необходимые электрические ограничения, предоставляет ссылки на существующие аналоги, консультирует тополога по возникающим вопросам.

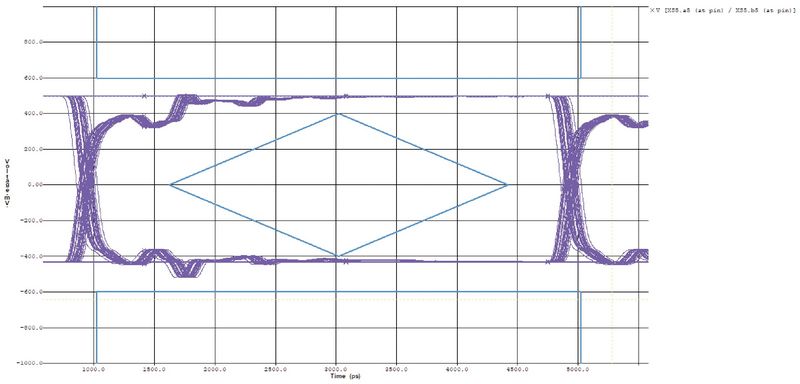

Электрические ограничения скоростных интерфейсов описаны в их стандартах. К таким ограничениям относятся: формирование функциональных групп критичных сигналов, назначение дифференциальных пар, учет требований по волновому сопротивлению (для дифференциальных пар и одиночных скоростных сигналов), требований по согласованной (одинаковой в пределах установленного допуска) временной задержке/длине трасс, по максимально допустимому количеству переходных отверстий, по порядку обхода выводов цепи (произвольный, последовательный, Т-образный, «звездой» и т. д.), по формулам, описывающим взаимную зависимость сигналов по отношению друг к другу (например, обязательное превышение задержки управляющего сигнала над задержками данных шины, гарантирующее полноценное считывание) и пр. При необходимости, практикуется пред - и посттопологическое моделирование для определения параметров линии передачи, для расчета номиналов согласующих пассивных элементов, для учета паразитного влияния соседних трасс (Рис. 5). В электрических ограничениях можно также задавать требования к слаботочным сигналам, минимизирующие наводимые извне помехи, и требования к сильноточным цепям, гарантирующие отсутствие перегрева. Поскольку модуль ограничений единый для всего проекта, электрические ограничения проекта могут задаваться непосредственно в проекте схемотехником (предпочтительнее) или топологом (по техническому заданию).

Топологические (конструктивно-технологические) ограничения, присутствующие во всех САПР ПП, устанавливаются топологом. Для узлов с высокоскоростными интерфейсами на основе требований их стандартов и опыта ранее выполненных проектов выбираются слойность печатной платы и ее структура в виде чередующихся проводящих и диэлектрических слоев с промышленными толщинами и заданными электрическими свойствами (в первую очередь, диэлектрической проницаемостью). Для функциональных групп сигналов с помощью специализированного калькулятора волновых сопротивлений в зависимости от величины требуемого сопротивления рассчитываются геометрические размеры трасс на выделенных слоях (ширины для одиночных сигналов и ширины / зазоры для дифференциальных пар), назначаются типы переходных отверстий. Все параметры определяются для платы в целом и, при необходимости, локально, т. е. в пределах отдельных зон, например, под корпусами с высокой плотностью выводов (корпуса типа BGA, LGA). Допускается использование нескольких типов переходных отверстий, отличающихся размерами и глубиной в теле платы — для всех слоев или только для определенных (т.н. сквозные, скрытые, слепые отверстия, микропереходы). Нестандартные структуры печатных плат и нетиповые ширины трасс / зазоры предварительно согласовываются с заводом-изготовителем.

Ранее примененные электрические и топологические ограничения можно экспортировать в абстрагированный шаблон для последующего использования в других проектах. Удобство заключается в простоте переноса отработанных, проверенных условий (назначений) и в несложной привязке импортированного шаблона к новым именам однотипных сигналов.

Базовые этапы разработки печатной платы заключаются в заведении ее контура и присоединительных отверстий, размещении элементов, трассировке соединений, проверке правильности выполнения заданных ограничений, экспорте данных для производства и для конструкторской документации.

После проработки всего узла (3D-проектирование) топологу выдаются конфигурация печатной платы, требования по зонам с ограниченной высотой элементов, зонам запрета трассировки, координаты краевых элементов, местоположение которых диктуется 3D-конструктивом (выходящие на панель соединители, индикаторы, кнопки и др.).

В размещении на плате основных элементов (ПЛИС, процессоров, микросхем памяти, локальных источников питания, сигнальных трансформаторов и пр.) наряду с топологом активно участвует схемотехник, который представляет взаимосвязи функциональных частей с оценкой их возможного паразитного влияния друг на друга и общей оптимальности трассировки. Он же впоследствии проверяет правильность прокладки критичных сигналов, расположение согласующих пассивных компонентов и фильтрующих питание дросселей и конденсаторов.

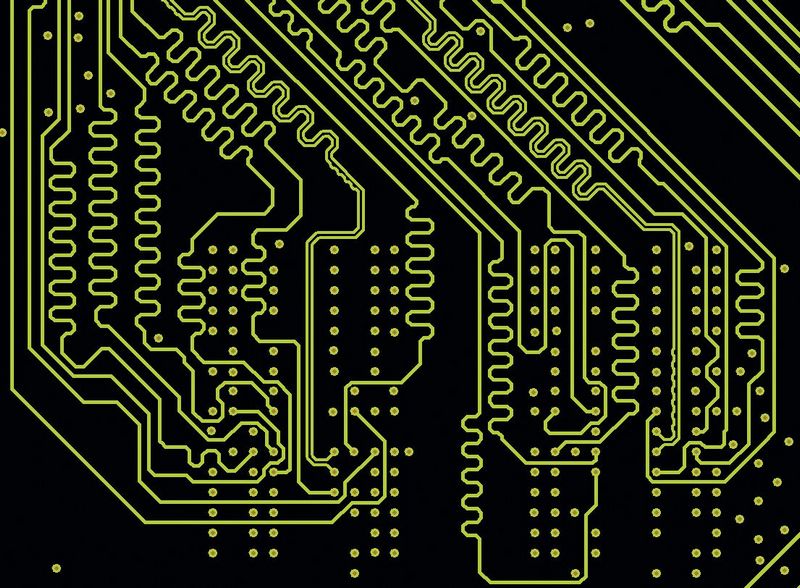

В структуре печатной платы сигнальные слои, как правило, чередуются со слоями питания, выполненными в виде сплошной металлизации для экранирования и являющимися опорными для сигналов с заданным волновым сопротивлением. Тополог придерживается общепринятой стратегии на этапе трассировки. Сначала он разводит сигналы высокоскоростных интерфейсов с последующим зигзагообразным выравниванием согласованных длин (Рис. 6), обеспечивает их экранирование в смежных слоях для кратчайшего пути обратного тока, затем трассирует аналоговые, высоковольтные, силовые сигналы, далее сигналы низкоскоростных интерфейсов, оставшиеся сигналы и цепи питания.

Для правильной работы с высокоскоростными интерфейсами в помощь топологам выпущен внутренний документ, обобщающий технические требования стандартов наиболее часто применяемых интерфейсов, содержащий пояснения к ним и примеры конкретных ситуаций. В документе также приведены общие топологические рекомендации по неразрывности пути обратного тока в опорных слоях, по снижению перекрестных помех путем правильного выбора зазоров печатного рисунка, по минимизации точек отражения внутри дифференциальной пары за счет задания ее допустимой асимметричности и правильного выравнивания составляющих ее трасс, по устранению неоднородностей в переходных отверстиях, достигаемому удалением неиспользуемых поясков металлизации во внутренних слоях, и др.

В проектах с использованием ПЛИС (особенностью последних является большое количество эквивалентных входных / выходных выводов) и в проектах с многовентильными логическими микросхемами активно практикуется процедура разрешенных взаимных перестановок (свопирование) выводов и вентилей. Такая возможность закладывается изначально в библиотечном элементе, а при топологическом проектировании позволяет существенно упростить трассировку за счет снижения зон перекрещивания трасс, являющихся местами потенциальных наводок. Итоговые результаты перестановок (свопирования) автоматически переносятся из топологии на электрическую схему соответствующей командой.

При работе со сложными и объемными проектами часто используется имеющаяся в САПР ПП возможность параллельной работы группы топологов над одной платой, когда каждый на своем мониторе видит в реальном времени действия своих коллег. Такой подход существенно сокращает (на 40-70%) рабочий цикл проектирования печатной платы.

Стабильная работоспособность узлов с высокоскоростными интерфейсами во многом определяется правильной реализацией заданных электрических и топологических ограничений, поэтому на завершающем этапе проводится двойная верификация их выполнения – топологом платы и назначенным проверяющим топологом. В обязанности последнего также входит общая проверка платы по регламентированным параметрам и правильность оформления заказа на ее изготовление.

Накопленный опыт работы в САПР ПП систематизируется на сервере, к которому имеют доступ все участники. Здесь размещены конфигурационные файлы и шрифты общего применения, внутренние инструкции (настройки под требования ЕСКД, подключение к табличной базе данных, правила получения bom-файла с необходимыми атрибутами, документ по работе с высокоскоростными интерфейсами и т. п.), выложены ответы на часто встречающиеся вопросы сотрудников, видеотека (ролики) по возможностям отдельных команд рабочих программ, тематическая подборка с профильных форумов в Интернете, статьи и видеоматериалы по проектированию высокоскоростных интерфейсов.

Так аккумулируются знания, в т.ч. по проблемным вопросам и путям их решения, что впоследствии, при повторении в других проектах, экономит время и средства. Есть выделенный куратор САПР ПП с опытом работы в ней, к которому в случае трудностей с проектом можно всегда обратиться за помощью.

Основные задачи куратора состоят в повышении эффективности использования САПР ПП и в создании для сотрудников удобной рабочей среды. С этой целью разработаны собственные программные утилиты, автоматизирующие рутинные операции в процессе и по завершении проектирования. Они используются при работе в схемотехническом редакторе, при подготовке заказа на изготовление печатной платы, при выпуске конструкторской документации. На предприятии периодически проводятся мероприятия по обмену опытом, практикуются выезды на учебу или на тематические семинары и конференции.

Для новых сотрудников подготовлены видеоролики для самообучения (создание нового проекта с заданием его настроек, выполнение основных операций, работа с базой данных и т. д.). Длительность каждого из них не превышает пяти минут для психологического комфорта и простоты освоения программ по принципу «посмотрел – попробовал выполнить самостоятельно». Также имеются электронные учебные пособия и типовые задания с пошаговым описанием их выполнения. Куратор САПР ПП, при необходимости, проводит учебные занятия с небольшими группами, после которых новые сотрудники приступают к заданиям в рамках текущих работ.

Описанная организация проектирования узлов на печатных платах, действующая в АО «НТЦ ЭЛИНС» на протяжении длительного времени (более 15 лет), хорошо себя зарекомендовала и может служить базой для сравнения на существующих предприятиях или основой для новых. Разработаны сотни узлов различной степени сложности, многие из которых воспроизводятся серийно. Использование технических возможностей САПР высокого уровня и регламентирование рабочего маршрута способствуют сокращению сроков реализации технологических проектов с высокоскоростными интерфейсами при соблюдении их гарантированного качества.